AD18 PCB Layout

PCB绘制流程:绘制原理图,元件引入封装并确认->原理图编译排错->网络表+元件封装导入PCB中->元件布局,布线考虑

EMI。

1、快捷键总结

所有键都是输入在英文状态下输入

| 快捷键 | 说明 |

|---|---|

| 原理图: | / |

| shift+f | 原理图中查找元件 |

| PCB图: | / |

| Ctrl+m | 测距,可使用shift+c取消选中 |

| Q | mil和mm切换(view->toggle units) |

| P ->P | 元件库放置引脚;SchLib元件库 |

| Shift +S | 信号线模式,PCB显示走线 |

| ctrl+shift+↑↓ | 上下层切换(小键盘+和-) |

| P->T | PCB快速进入布线 |

| 23 | PCB中2D和3D模式切换 |

| * | 添加过孔 |

| J->C | PCB中查找元件 |

| shift多选几个布线网络 | 总线式布线 |

| ctrl+高亮显示的网络 | 高亮网络 |

| Shift+H | 布线实时跟踪显示 |

2、规则设置

阻焊层大小设置–>

Rules->mask->soldermaskexpansion->All->expansion 0.05mm覆铜到板边距离设置–>

Rules->electrical->clearance->custom query填写inpoly minimum clearance 0.4mm覆铜到

SMT的mark点圆形避空区域规则设置。SMT网络–>GND网络距离设置1.1mm,Design–>rules–>plane–>power plane clearance–>新增规则planeclearance_SMT在where the object matches选择net–>smt,再设置clearance填写3mm即可。覆铜接地的十字脚规则设置:

Design–>rules–>plane–>polygon connect style–>新增规则Polygonconnect_xxx在where the first object matches选择ALL,在where the second object matches选择ALL。再设置Air gap width填写0.2mm,conductor width填写0.45mm即可。classes类的设置:

design——class中 建立differential pair classes,就是建立差分类,add class就行,建立一个为90OHM的差分对类确定OK。选择右下角的PCB-PCB,在下拉框里选择differential pair class,对上一步添加的差分对添加net,选中90OHM在下方的Add处添加差分对线可以分别命名为90OHM_1,和90OHM_2差分对规则设置:

Design–>rules–>differential pairs routing–>Diffpairsrouting在where the object matches选择diff pair class–>选择自己建立的差分对类,再设置线宽,线距离等。差分线设置规则设置完成后可以使用快捷键对差分线进行走线,快捷键

UI即可就对差分线进行走线,同时可以利用弧形走线(Shift+空格,英文输入法下),将差分线走为等长。如果画的不对可以选择中走线按下TAB可对线网络选择然后再删除。

3、PCB LAYOUT

3.1、元件布局常规

- 同一功能模块的元件尽量布局在同一区域范围,比如不可将输出端的元件布局在输入端的区域,或高压区的元件布局在低压区。

- 尽量将元件贴近芯片管脚,使线路做到尽可能短,但芯片管脚周围

3mm内不可放置元件,否则在维修或焊接时带来麻烦。 - 元件里板边至少要留

3mm的距离特别是插件元件周围,防止在安装过程中损坏板边元件。 - 预留安装孔和定位孔,并且在这两类孔周围

3mm内不可布置元件。 - 同一区域的有极性电容或同一类型的元件最好布局成同一方向的焊接方式,以方便在生产加工时减少焊接错误。

- 去耦电容尽量布置在芯片的电源管脚最近处,板上可调元件尽量布局在板边周围以方便调节,并且注意不能被周围的元件结构遮挡调节孔。

- 相临层信号线尽量走正交方向,比如顶层布线为水平,底层布线应该为垂直。

- 高频信号应该尽量短。一般高频也不要过孔(过孔在高频情况下有电感效应)。要做阻抗分析,做到阻抗匹配而且尽量等长。

- 输入、输出信号应该尽量避免相临平行走线,防止反馈耦合。

- 把主控芯片,LED,插脚,接线端子等放在正面,把电容电阻,一些常规的贴片小芯片放在背面;注意:一般端子,开关,按键灯放在板外侧,LED放在正面方便观察

- 根据主控芯片的引脚位置,把正面的芯片和插脚位置排好;芯片、差分线、晶振等重要的部分下方不要布线,并且晶振尽量紧贴芯片。

- 把相临的电容电阻等,见缝插针,放在芯片附件。滤波电容等要靠近芯片电源。

D+,D-差分走线要平行等长,周围用GND,地线包围住。

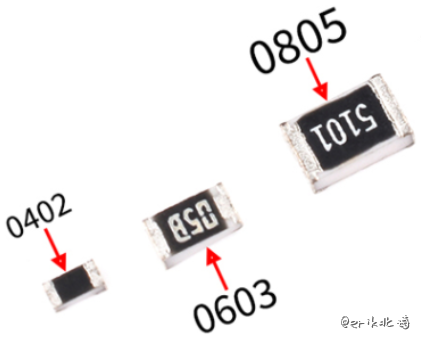

3.2、电阻电容的封装选择

电阻电容的封装:

RES1206 0805 0603 0402 0201 01005,CAP1206 0805 0603 0402 0201 01005,不同的封装对应不同的功率。

1uf以下的使用0201的电容10uf以下的使用0402的电容10uf以上的使用0603的电容47uf以上的使用0805的电容- 电阻一般在电源附近的选择使用

0603 - 一般的信号线或者不靠近电源的使用

0402 - 使用电阻一般的是大概估算电流大小,计算功率,不同封装的点阻对应的功率不同,一般

1/8或1/4等。

4、实际案例中的问题

4.1、焊盘间出现规则问题标绿色

Tool->Reset Error Markers

4.2、设置PCB板子形状

Shift选中Keep-out layer所有的线,线需要是封闭的图形,Design->Board shape->Define from selected objects(快捷键:D-S-D)。(使用的AD18已取消了keep-out layer层当做板边,不再具有机械属性,只有禁止布线属性,所有的keep out不能用来做板边。默认File->inport->dxf文件中板边缘是machinery1层,但是可以通过鼠标右键Place->keep-out->Track手动画keep-out;

先选择好一个封闭的板边,然后点击命令TOOL–>convert–>convert select primitives to keepouts即可转换为Keepout layer,同理也可以将keepout layer转换为机械层等。

如果板内有孔之类的不是板的内容部分,现在对应的Track,在Tool->convert->create board cutout form selected primitives(快捷键:T-V-B),将其去除;[cutout挖剪图形]

4.3、覆铜

Tool->polygon pours->polygon manager在管理中->create New Polygon from->board outline->TOP Layer(Bottom Layer)->链接net(GND)->pour over all same net objects同时选中Remove Dead Copper

4.4、将已经画好的PCB元件封装导出方法

Design->make PCB library

4.5、AD中编译出现off grid at/off grid pain时如何解决

- 首先,不是原理图电气连接出现问题,而是元器件或是器件

PIN脚没有和栅格对齐造成的 - 选中

off grid的元器件 - 单击鼠标右键

- 在弹出的对话框中选择

Align,出现二级菜单,选中alig(align:使成一线,对齐;align to grid:对齐到栅格)

4.6、画封装时防止焊盘矩阵

选择一个焊盘,将焊盘cut掉,随后按E—>A选择粘贴矩阵设置即可。

4.7、layout时将不必要的body进行hide

在pcb文件中按L到达select PCB View configuration中,第一页可以set board layouts and colors,选择第二页中的show/hide,选择polygons&3D bodies&fills将其选中hide。

4.8、Layout时等长布线和蛇形布线

设计中常遇到等长布线的情况,例如差分信号,了解差分信号原理都知道,差分信号是根据同一时刻两个信号线之间电压值来传递数据的,如果线长度不同,信号接收端接收的信号压差就会出现错误,这样看来等长布线就很重要了,蛇形布线只是等长布线的一种方式而已。

Design–>classes–>net classes右击Net classes –>add class ,将需要等长处理的网络添加到右边格子中,点击close

等长布线的规则设置(拐角的长度、宽度)在布蛇形线时,只能在已经布好的线上修改,提前布好需要等长处理的线,然后选择一根较长的线作为基准,单击快捷键T、R点击其中一跟线(不要点基准线,基准线不需要实际的操作)按下table键,进行蛇形规则设置。选择from net,在右边基准线的网络,设置完成后点击ok。

在蛇形布线时,按快捷键1/2/3/4可以随时可控制蛇形线的形状。

- 快捷1&2—>改变蛇形线的拐角和幅度

- 快捷3&4—>改变蛇形线的宽度

- 快捷,&。–>改变蛇形线的幅度

4.9、差分布线

AD中自带的差分信号Differential pair class(差分对类)

在AD软件中右下角点击PCB,在弹出的项目中勾选PCB项目,此时会出现PCB的区块,找到differential pairs在下面找到Add按钮,此时有两条对称走线,点击新添加差分走线规则,在对话框中,positive net即阳极网络,negative net即阴极网络,设置完成后即可在pcb对应的层中鼠标右键,选择interactive differential pari routing布线。

4.10、原理图导入到PCB

在原理图中导入PCB,

Design->update PCB Document xxxxx.pcbDoc,在分别点击Vaildate change和execute change;PCB中导入原理图网络,在PCB中选中菜单

Design->import change form xxxxx.prjPCB;

4.11、PCB板中添加LOGO

- 方法一:需将

logo图片变成单色位图黑白BMP格式后导入到word当中,然后ctrl+c复制,在PCB文档中的top overlay按ctrl+v粘贴即可。 - 方法二:同时也可以使用

script导入的方法,Altium Designer 2013 PCB Logo Creator.rar压缩包的script,在AD中File–>run script–>browse–>选择PCBLogoCreator.PRJSCR,再选择Converter.PAS,则弹出导入图片的框,简单设置后即可导入。导入后生成的图标是零散的,这时候就可以使用组合功能,选择要组合的器件,点菜单Tools_Convert_Grate Union from Selected Objects就会生成联合体。

4.12、PCB导出gerber,针对工厂做哪些处理

- 尺寸标注:标注信息全部都放在机械层,单击

place->dimension->菜单下有各种尺寸标注工具。 - 各层加层名:便于打印出PCB自己知道图中各层信息,便于加工工厂PCB文件底部知道底片作用, 单击菜单

place->string进入放置字符模式,再按TAB进入字符串属性设置,在properties设置栏的Text栏内点击下拉菜单,从中选择.layer Name,在layer栏内选择放置的层。点击OK完成放置。加好层名输出gerber文件会自动在各层上显示名称。 - AD拼板的时候,使用特殊粘贴。一般板边为

5mm,定位孔为2-3mm,拼版时候线段精确移动快捷键M–>MOVE根据X or Y或根据点移动等。 v-cut是分连片的专有名词,一般有v-cut的深度和角度。- 添加泪滴焊盘:

tool–>teardrops...在working mode选择add,objects选项选择ALL,scope中选择Via/TH pad点击OK即可。

4.13、AD18 keepout层画线

AD18中如何将画线布到keepout 层,先选择画的线部分,在TOOL工具中选择convert–>convert selected primitive to keepouts,同时也可以将keepout layer层转换为机械层,选择需要转的部分,F11将层转换为TOP layer层,在使用Tool–>convert–>convert selected keepouts to primitive 命令后再F11转为mechanical层即可。

4.14、原理图和PCB联动

快速布局,将sch和pcb同时打开,在pcb或sch标题右键选择split verticel分栏显示,在tool中选择cross select mode使元件在sch中选择并pcb中高亮。

4.15、pcb导出成为PDF文档

File–>smart pdf–>current document(xxx)–>取消勾选export a bill of materials–>在NAME栏位(multilayer composite print)右键选择create assembly drawing此时就将TOP和bottom层分开了,top层中可以添加需要的layer和删除不需要的层,在某些层也可以选择层中某些东西可见与不可见。

在bottom层的mirror那个表签下选择勾上让其镜像–>在area to print那一栏中选择specific area点define框选需要打印的部分。–>pcb color mode那一栏中选择color或者greycale(一般选择彩色)输出即可。

4.16、PCB线宽和过孔

先计算电流,一般情况下为1A电流为1mm的线宽。一般信号线宽约0.2mm,最小为0.18。差分线和电源线要大些。差分线0.38,电源线0.4mm,线间距为0.2mm,过孔外径为0.4mm,内径为0.25mm。

4.17、更新封装

AD18封装PCBlib更新后,需要更新到PCB档案中,(封装更新到PCB)方法如下。在PCBlab库中修改好封装后,在该封装的选择情况下。点击TOOL–>update pcb with current footprint即可更新到pcb中。

4.18、AD批量添加覆铜批量过孔

双面板在顶层和底层之间批量添加过孔可以加强抗干扰,手动添加太累人,AD中有一个“过孔矩阵”的功能。工具->via stitching->add stitiching to net :(选项面板选择网络为GND,栅格大小,Hole size,diameter大小等)即可批量添加。

- Grid:1.5mm

- Hole Size:0.25mm

- Diameter:0.35mm

- Default via/pad clearance:0.12mm

- 如果想删掉这些批量的过孔,拖动其中一个,按DEL>即可全部删除。

4.19、多个原理图导入到多个PCB中

原理图中的Project菜单->show differences在选择文件中choose Documents to compare 左下角选择高级模式Advanced Mode,在其中选择一个SCH,并在另外一个中选择对应的PCB文件,选择OK。这时候在对话框中列出了SCH和 PCB的对应关系,任意在空白位置点击鼠标右键,选择Updata all in >> PCB Document XXX.PcbDoc,把所有不同的SCH不同转入到PCB中,点击create Engineering Change Order 在弹出的对话框中选择validate changes->execute changes更新到PCB中。

4.20、检查布线是否完全

Report->Board information,单击report,鼠标拉到最后一行找到routing information,单击report,查看报告布通率为100%即表示没有未连接的。

而AD18版本换位置了,在视图右边的properties(如果没有,可以在右下角的panels面板中打开),打开后下滑可以找到大大的report,点击report下滑找到routing information,单击report查看。

4.21、覆铜完成后,修改元件或者布局,重新覆铜

1.不用重新覆铜,如果修改了元件布局或者走线,双击铜皮,然后再确认更新,就行了。

2.使用快捷键T——G——–A,直接到参数设置里,把覆铜修改后自动重覆。勾上。这样每次修改自动更新。

5、元件

5.1、TVS

TVS:瞬态二极管(transient voltage suppressor)是一种二极管形式的高效能保护器件,当TVS二极管两级受到反向瞬态高能量冲击时,它能以10^-12^次方秒级的速度将其两级的高阻态变为低阻态,吸收高达数千瓦的浪涌功率,使的两极电压位于一个预定值,有效保护电子线路中精密元器件,免受各种浪涌脉冲的损坏。

TVS和齐纳二极管都能用作稳压作用,但齐纳二极管电流更小,大于10V的稳压只有1mA,相对于齐纳二极管击穿电流要大不少,但是齐纳二极管稳压精密度可以做到更高。

5.2、FB

FB:磁珠(ferrite bead)磁珠专用于抑制信号线,电源线上的高频噪声和尖峰干扰,还具有吸收静电脉冲的能力。