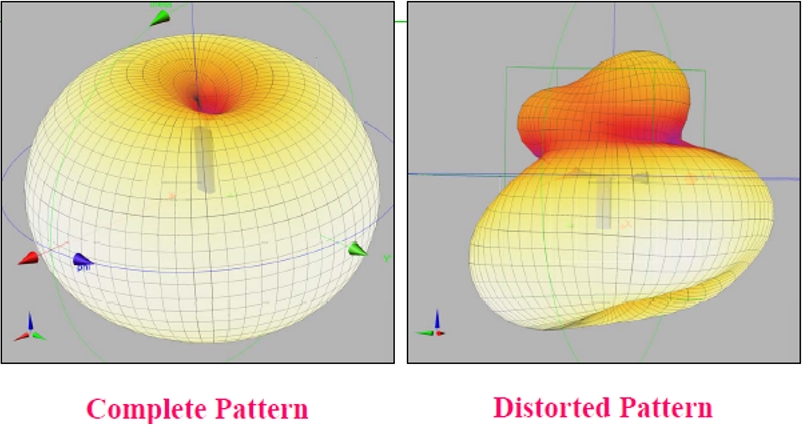

RF产品获得的无线射程主要取决于天线的设计、塑料外壳以及良好的PCB布局。

1、2.4G天线

阻抗控制在硬件设计中是一个比较重要的环节,针对不同信号系统有不同的特征阻抗值,比如75ohm、100ohm、90ohm、50ohm等,而对频率较高的RF信号来讲,最常见的是50ohm的阻抗控制。

在实际的PCB设计中,考虑到芯片的RF特性、实际PCB生产工艺除了需进行PCB RF传输线的阻抗控制外,在硬件设计上通常还需添加一些匹配网络电路用作RF的调试,一般说来,其作用大概为以下几种:

- 谐振频率以及带宽的调整

- 功率、EVM、ACLR、PA电流、传导杂散和辐射杂散等指标的调试等

一般情况下天线的导体的波长为λ/2,其中λ为电信号的波长。信号发生器通过一根传输线(也称为天线馈电)在天线的中心点为其供电。按照这个长度,将在整个导线上形成电压和电流驻波。

输入到天线的电能被转换为电磁辐射,并以相应的频率辐射到空中。该天线由天线馈电供电,馈电的特性阻抗为

50Ω,并且辐射到特性阻抗为377Ω的空间中。

所以在PCB几何形状,有两个非常重要的事项需要注意:

天线长度

天线馈电

长度为

λ/2的天线被称为偶极天线。但在印刷电路板中,大多作为天线使用的导体长度仅为λ/4,但仍具有相同的性能。用于

2.45GHz的1/4印刷单极天线天线长度:L = 92mm / 4 = 23mm

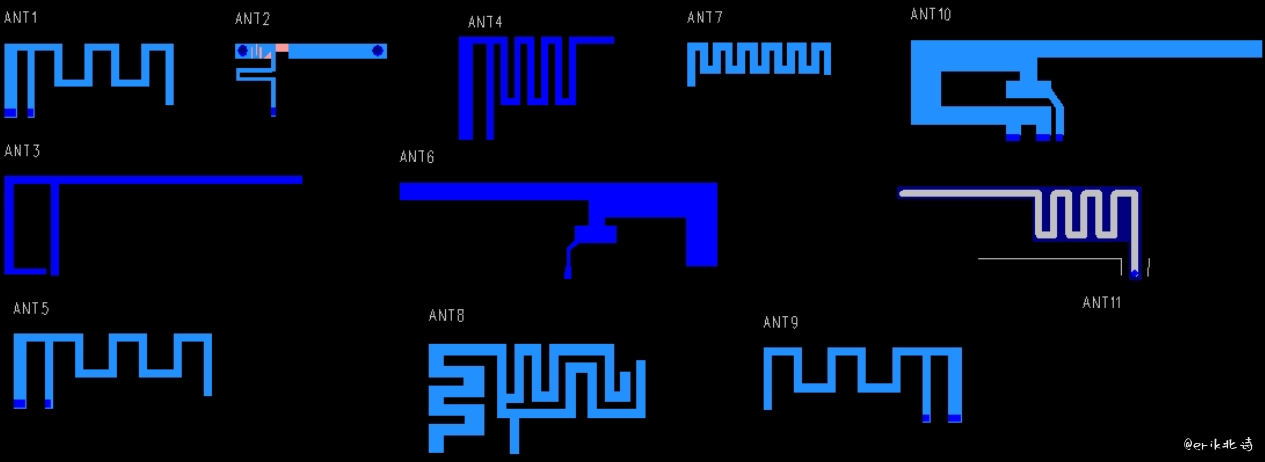

通常板载2.4G PCB设计封装库如下图所示。

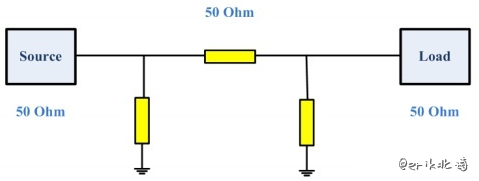

2、阻抗匹配的模型

工程师大都遇到过匹配阻抗的问题,通俗的讲,阻抗匹配的目的是确保能实现信号或能量从信号源到负载的有效传送,其最理想模型希望Source端的输出阻抗为50Ω,传输线的阻抗为50Ω,Load端的输入阻抗也是50Ω欧姆,一路50Ω下去,这是最理想的。

然而实际情况是一路都不会是50ohm,这个时候就需要若干个阻抗匹配电路,而匹配电路就是由电感和电容所构成,这个时候我们就需要使用电容和电感来进行阻抗匹配电路调试,以达到RF性能最优。

3、电感电容的高频特性

天线匹配网络所使用电感电容工作在2.4G高频率下,所以要解决电感电容解决高频的性能问题,所以就需要先了解下电容和电感这些器件在高频的特性。

3.1、高频电容

对电容器,是用平板表面积与平板间距的比值来定义其容量:

$$

C=\frac{\varepsilon A}{d}=\varepsilon_0 \varepsilon_ r \frac{A}{d}

$$

A代表平板表面积,d代表平板间距,理想情况下在平板间没有电流流动

但在高频信号通过时,电容器平板间的实际电介质存在损耗(也就是板间有传导电流流动),所以,电容器的阻抗需要表示成电导和电纳的并联组合:

$$

Z=\frac{1}{G_e +jwc}

$$

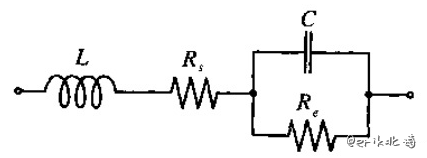

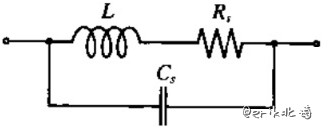

考虑电容器寄生引线电感L,描述引线导体损耗的串联电阻$R_s $及介质损耗$R_e =1/G_e$,高频电容器对应的电等效电路如图所示(高频电容等效电路)。

3.2、高频电感

而对电感而言,在射频电路中经常使用的电感为线圈结构,其线圈是用导线在圆柱体上绕制而成,线圈除了具有与频率无关的电阻之外,它还存在一个电感,而临近的绕圈间存在着分离的移动电荷,所以它还存在一个寄生旁路电容。

考虑到寄生旁路电容$C_s$和串联电阻$R_s$后,电感器对应的等效电路模型如图所示(高频电感等效电路)。

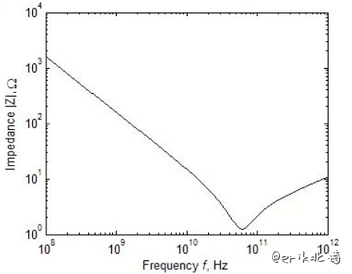

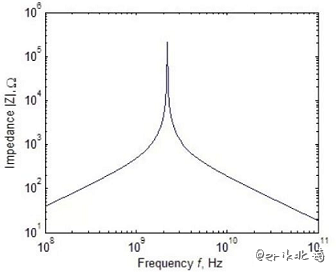

在高频时,电容器中的电介质产生了损耗,所以电容器在谐振点前,呈现的阻抗特性与频率成反比(如图高频电容阻抗频率曲线);

而对电感器而言,当频率接近谐振点时,高频电感的阻抗迅速提高,当频率继续提高时,寄生电容C的影响成为主要的,线圈阻抗逐渐降低(如图高频电感阻抗频率曲线)。

所以,一个实际电感或者电容并不能简单用电感量或电容量来衡量,而应该将其当成寄生旁路电容C、串联电阻R、寄生电感L的综合效应,这个时候通过一个等效网络去模拟要更为合理,当然,具体使用时,有时还需考虑集总参数和分布参数电路模型。

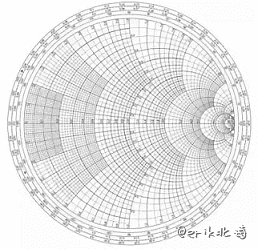

4、Smith圆图在RF匹配电路调试中的应用

Smith圆图上可以反映出如下信息: 阻抗参数Z,导纳参数Y,品质因子Q,反射系数,驻波系数,噪声系数,增益,稳定因子,功率,效率,频率信息等抗等参数。

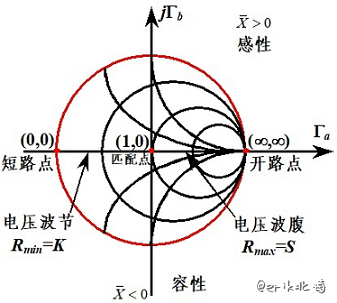

如下smith圆图:

阻抗圆图的构图原理是利用输入阻抗与电压反射系数之间的一一对应关系(如阻抗图圆所示),将归一化输入阻抗表示在反射系数极坐标系中,其特点归纳如下:

- 上半圆阻抗为感抗,下半圆阻抗为容抗;

- 实轴为纯电阻,单位圆为纯电抗;

- 实轴的右半轴皆为电压波腹点(除开路点),左半轴皆为电压波节点(除短路点);

- 匹配点(1,0),开路点(∞,∞)和短路点(0,0);

- 两个特殊圆:最大的为纯电抗圆,与虚轴相切的为匹配圆;

- 两个旋转方向:逆时针转为向负载移动,顺时针转为向波源移动。

导纳圆图与阻抗圆图互为中心对称,同一张圆图,即可以当作阻抗圆图来用,也可以当作导纳圆图来用,但是在进行每一次操作时,若作为阻抗圆图用则不能作为导纳圆图。

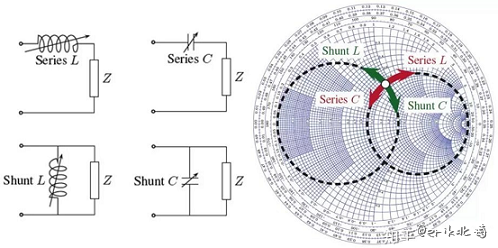

Smith圆图中,能表示出一些很有意思的特征:在负载之前串联或并联一个可变电感/电容,电路图如(图smith轨迹变化规律)左侧4个图所示,将得到Smith圆图上右侧的几条曲线。对应Smith阻抗圆及导纳圆,其运动轨迹如下:

- 使用Smith阻抗圆时,串联电感顺时针转,串联电容逆时针转;

- 使用Smith导纳圆时,并联电感,逆时针转,并联电容顺时针转。

5、匹配电路调试的注意事项

以上串并联元件对应的smith图上的运动轨迹可作为调试的参考及对结果的初步判断,而至于RF匹配电路实际调试过程中的注意事项,一般而言有五项:

电感/电容值不要过小,原因是要维持匹配的稳定性,因为电感/电容值会有误差,以电容为例子,大概有

±0.1pF的误差,如果是一个容值为0.3pF的电容,则误差高达33%,其容值范围为0.2pF~0.4pF,这可能会导致每片PCB的Tx/Rx Performance不一致,进而影响工厂量产时的良率。落地电容值不要过大,是因为依照容抗公式,电容值越大,容抗越小,因此落地电容值过大,则可能会让信号都流到地端。

$$

Z_c=\frac{1}{jwc}

$$

电感/电容值不要过于冷门,原因是方便备料。若是常见的值,则所有厂家都会有,量产过程中,避免出现厂家缺料的情况。

尽可能设计成

Low Pass Filter,原因是这样可以抑制谐波。常用的Low Pass Filter的组合如下图:

- 对一般消费电子产品而言,匹配电路整个频带的

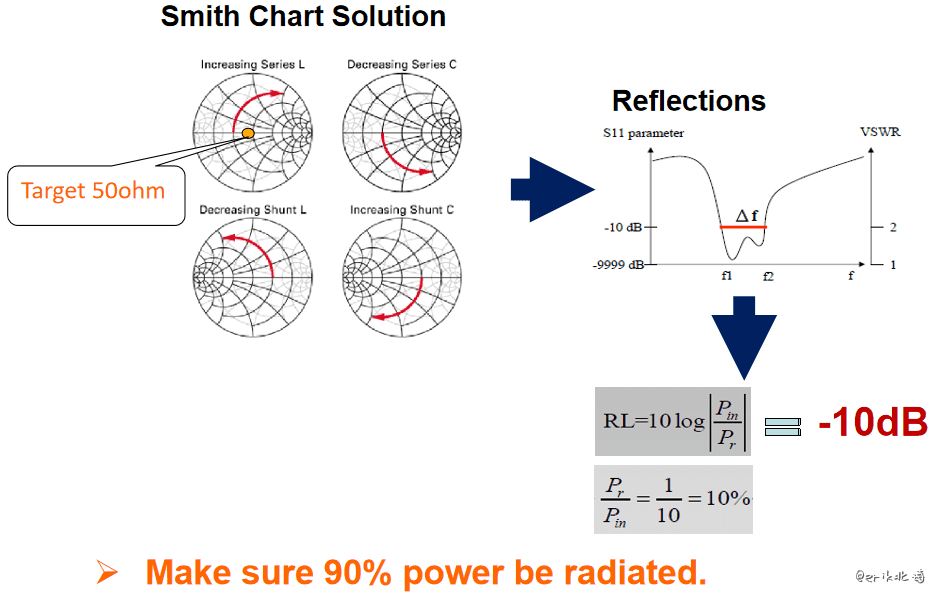

smith原图轨迹需落在VSWR=2的圆内,且其整个频带的阻抗轨迹尽可能收敛,这是最重要的原则,上述步骤,是以单一频率点来做匹配,但最后看整个频率范围内的Smith Chart轨迹,才能决定这一组匹配值可否采用。(如下两图所示)

6、网络匹配知识点

射频天线模块的天线输出口ANT端,可以被称为source端,天线可以被称为Load端。

6.1、反射系数

S11实际上就是反射系数,不过它特指一个网络端口的反射系数,反射系数描述的是入射电压和反射电压之间的比值,而回波损耗是从功率的角度看待问题。RL=-S11

反射系数:信号沿传输线向前传播,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。对于信号来说,它不会区分到底是什么,信号感受到的只有阻抗,如果信号感受到的阻抗是恒定的,它会正常向前传播,只要感受到阻抗发生变化,不论是什么引起的(可能是中途遇到电阻、电容、电感,过孔、PCB转角、接插件),信号都会发生反射。

($\Gamma$ = gamma大写)reflection coefficient/反射系数gamma:

$$

\Gamma=\frac{Z_l-Z_0}{Z_l+Z_0}

$$

其中Z是归一化负载值,即ZL/Z0。当中,Zl是线路本身的负载值,Z0是传输线的特征阻抗(本征阻抗)值,通常会使用50Ω。

6.2、VSWR

VSWR电压驻波比:为测量泄露量,提出的术语VSWR,VSWR是描述匹配情况的数字度量,匹配越好,泄露越小。VSWR公式很复杂,没有度量单位,表达式是X:1.X越大,泄露越多。

1.0:1完美匹配,没有泄露的软管,不可能制成 回波损耗:无穷大1.4:1优良匹配,很小泄露,通常作为设计目标 回波损耗:15.62.0:1良好匹配,可接受泄露量。 回波损耗:9.510:1可怕的匹配。 回波损耗:1.7

回波损耗,以db为单位,可以看出VSWR越大,回波损耗越小。

6.3、折返损耗(Return Loss)

折返损耗(Return Loss) = 0dB,表示全反射,沒有功率传送到负载。折返损耗 (Return Loss)代表反射功率的大小,是相对于VSWR的另一种指标的表示法。(当VSWR = 2时,Return Loss = -10dB)

6.4、感性/容性负载

如果

(WL-1/WC)>0,称为”感性负载”,如果(WL-1/WC)<0,称为”容性负载”。

如果电路中只有电阻,它只会影响信号幅度;如果电路中不仅存在电阻,还存在电感及电容时,不仅会影响信号幅度,相应的相位、频率特性也会发生变化。

6.5、实际调试需记忆内容

如何快速记住smith圆图:在一个复平面内,以实部为X轴、以虚部为Y轴,表示任意一个复数,将复平面扭曲变成圆。短路点(左边)和开路点(右边)分别扩散出小圆。左边圆是导纳图,右边圆是阻抗图。上半圆为感性负载,下半圆为容性负载,中间横线为纯电阻。

串联器件看阻抗图:串联电感顺时针移(增加感性),串联电容逆时针移(增加容性)

并联器件看导纳图:并联电感逆时针移(增加感性),串联电容顺时针移(增加容性)

7、设计建议

对于靠近PA或者DUP等射频前端器件的匹配网络大家都会预留,尽量不要因为产品尺寸较小又需要设计PCB板载天线,为了节省空间而省掉了靠近天线端的匹配网络,从而导致在RF性能的优化过程中或者认证要求的杂散测试中束手无策。在实际的电路设计中,还是建议预留匹配电路,不管是射频前端还是后端的部分。

8、阻抗匹配实践

根据理论基础进行实践,我已经调试成功,板载天线信号效果超好!!!

8.1、PCB板载天线阻抗匹配步骤

目的:为了保证信号或能量有效的从

信号源传到负载而不会有信号反射回来源点,从而提升能源效益。

天线调节仪器使用大致分为5步:

- 校准网络分析仪,校准到连接线到板上的射频线缆(延长线补偿)

- 通过网络分析仪测量原始阻抗

- 借助史密斯圆图进行阻抗匹配

- 选择合适的电容电感焊接到PCB上

- 测量无线芯片的输出和输入是否满足要求

8.2、网络分析仪器校准

仪器校准工具三端,分别为O,S,L对应为开路端open,短路端short,Load负载50欧姆端match。

首先Preset恢复预设,E5062A menu目录下:

1 | Menu───┐ |

设置频段,一般是2G到3G段。因为一般用的段都在2G到3G频段。点击start设置开始段。点击marker设置三个make点分别频段如下:

- 2.402G——-起始

- 2.441G——-中间(增加39)

- 2.480G——-某段(增加39)

菜单下选择

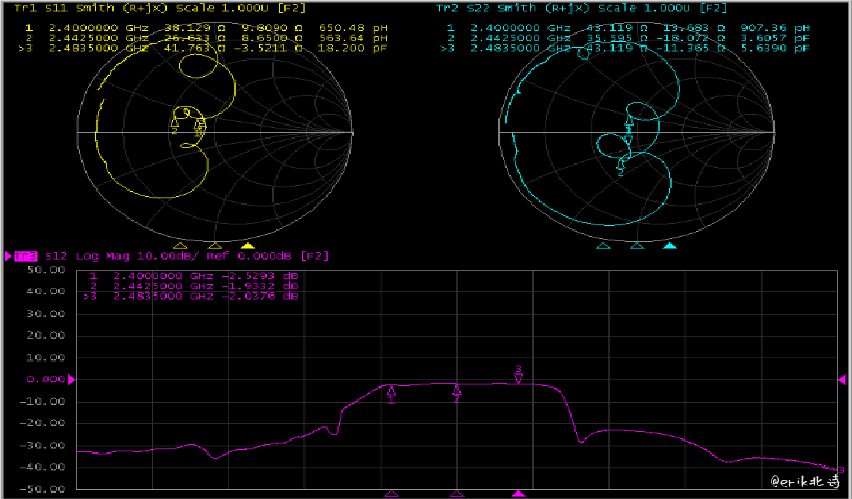

S11(S11表示一进一出,S21表示一进二出。),设置S11两个display(display菜单)显示图像。再点击format设置图像格式。一个为smith图像(R+jX),一个为log Mag图像10db/ref 0db。设置方法为点击display选择一,再添加smith,选择二在添加log Mag。(调节时就尽量将三个make点调节到50Ω点,log mag在-10db以下)

将校准工具O,开路端接入测试仪,点击开路端,软件记录,

再将校准工具S,短路端接入测试仪,点击短路端,软件记录,

再将校准工具L,负载端接入测试仪,点击负载端,软件记录。

- 取下校准仪器,这个时候,软件就能将三个

mark点显示到中间端50Ω。(smith图左边是短路,右边是开路端)

8.3、延长线补偿

点击面板上的cal(calibration/校准)选择port 1 extension(扩大,延伸)对所接的延迟线进行补偿,将延长线接入,滚动圆盘,使三个mark点都聚集到开路点,这个时刻三个点的阻抗是最大的。即可完成对延迟线的补偿。补偿完成后即可后续的测试。

天线端的π形match部分接线出来,一定要接到match电路前,包含所有的match部分电路。

原理图设计时,需要在天线接头与模块的天线引脚之间预留一个π形匹配电路。天线阻抗是受电路板铺地、外壳、安装角度等因素影响,预留

π形匹配电路是为了天线严重偏离50Ω时,将其纠正到50Ω,理论上天线阻抗在任何值,都可以通过π形匹配电路匹配到50Ω,而实际是电感电容有内阻,内阻会吸收能量如果天线阻抗太小或大的话通过匹配电路匹配到50Ω去就失去了意义,原因是大部分能量消耗在匹配元件内阻上。

8.4、天线端开始调节

流程简要:将天线匹配电路连接至

IC端线路割断(匹配电路最后一个元件的pad点,越靠近越好),从天线端第一个匹配电路元件开始接入cable线,放入外壳中,测天线阻抗。根据阻抗值依次序往天线后端加入匹配元件,cable线位置也靠近匹配元件后方。直至接近50Ω。友情提要:一般情况下,匹配元件最好串联电感,并联电容。这样有利于

EMI。

确保90%的功率被辐射,射频路径调谐方法示意:

- 在pcb

π 型网络上焊接一个0Ω的电阻(不能使用焊锡直接短路,因为从高频上看利用焊锡直接短路,会有寄生效应,测出来的原始阻抗不准),把整机待测的设备(带上外壳)用SMA连接起来,然后接到网络cable上面,观察此网络分析仪上典型的2402Mhz,2441Mhz,2480Mhz频点的阻抗大小,测出原始阻抗。

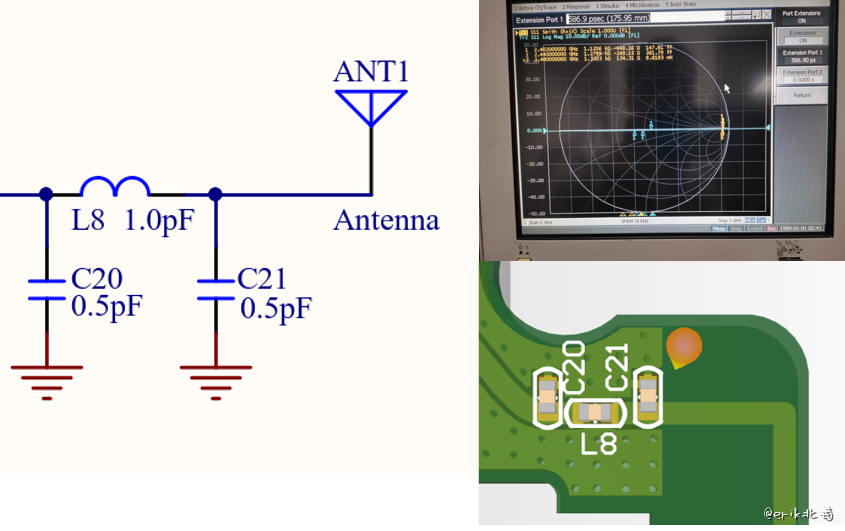

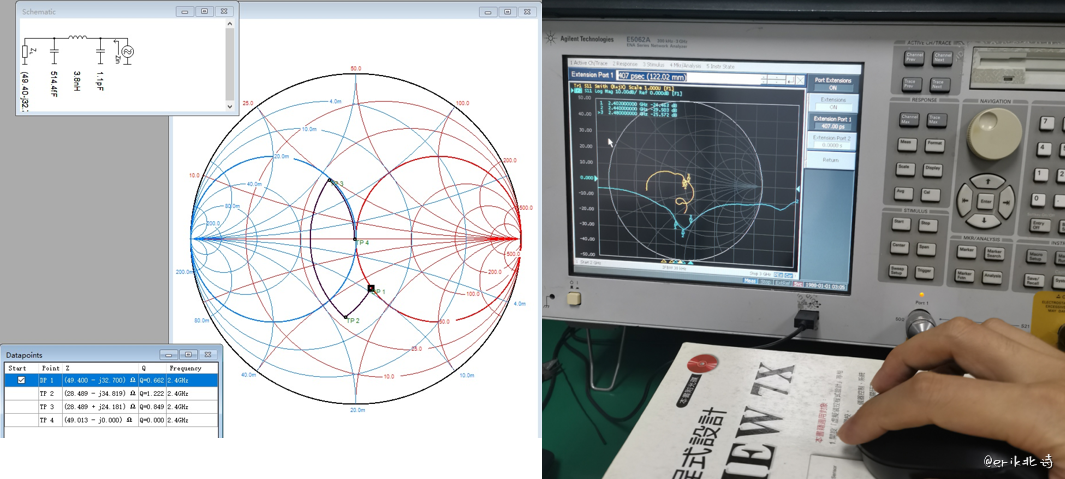

- 如上图所示,

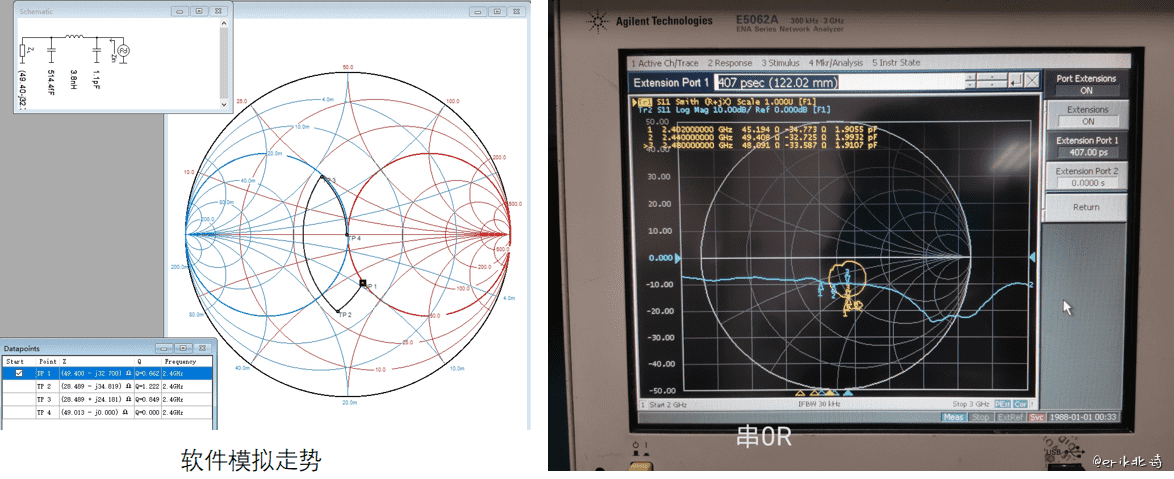

L8位置串接0R,其他不接任何元件,测试出原始天线所在位置。用软件进行模拟串并连电容电感的走势。

- 此时发现在

smith图圆上下端,呈容性。三个典型频点阻值太小。按照一般做法,可以串电感回50 Ohm点,一起开发的台北工程师使用的是这种方法。我现在尝试另一个方法,先并一个0.5PF电容。(注意cable连接的位置,需要连接到0.5 PF电容的引脚上)

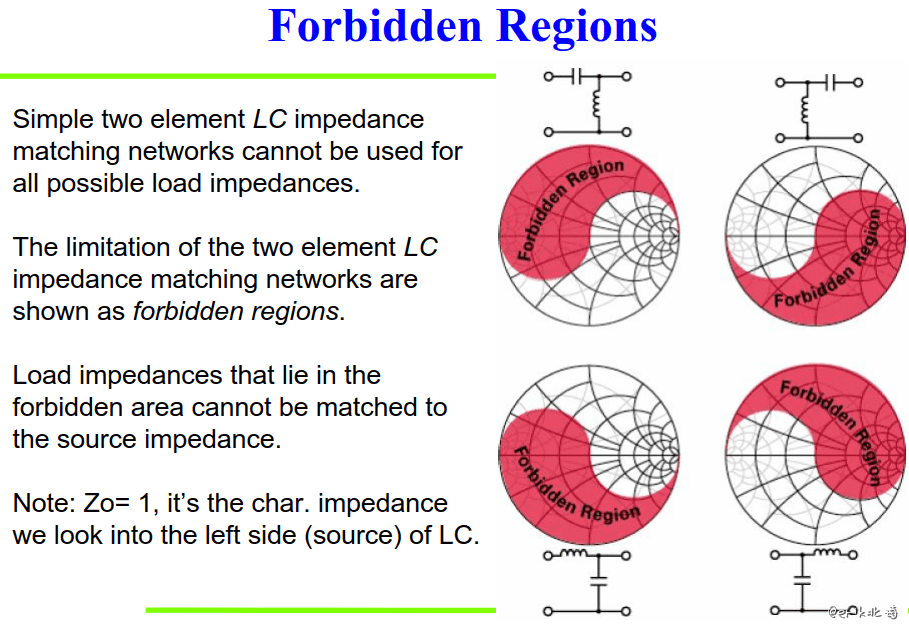

- 参考如上图适宜的区域,(红色的部分为禁区)选择适应的方式。

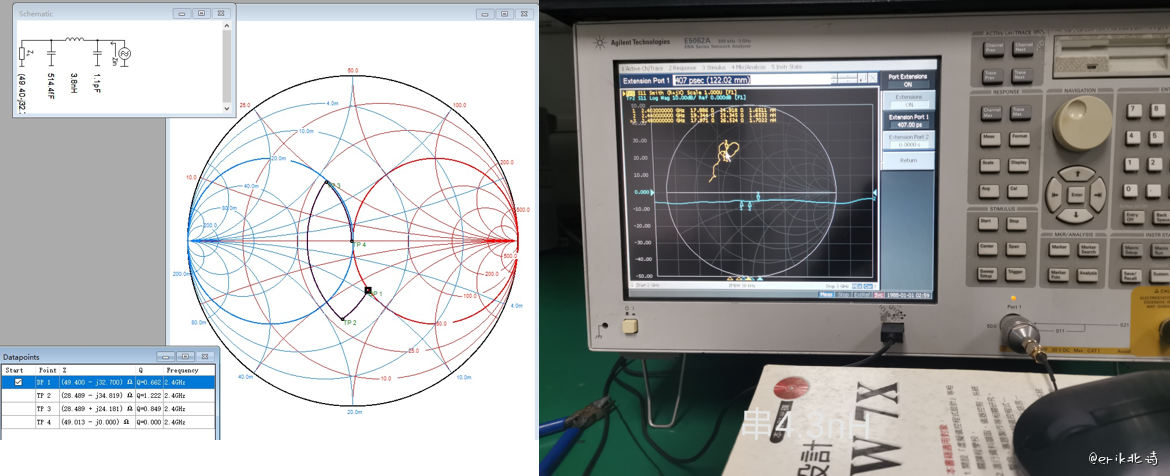

L8串4.3nH电感,由于原來的0R也有电感,所以实际比理论稍大, 如下图所示:

- 随后在

C20并1PF电容,其效果图如下所示:(尽量考虑实际的使用情况,加上手后的测试图)

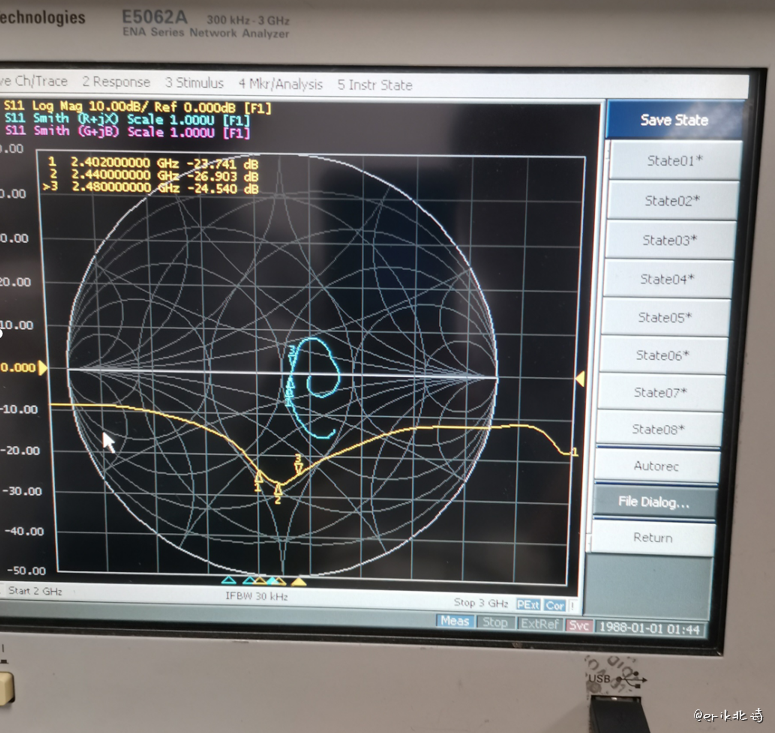

- 由实际测试出的网络分析仪图像进行观察(如下图所示):

RL = S11 = 反射系数

- RL:2402MHz:-23dB

- RL:2440MHz:-26dB

- RL:2480MHz:-24dB

根据以上天线调试1-7步,匹配网络相关值:Match: C21=0.5PF,L8=4.3nH,C20=1PF,实机测试power也与预设power基本一致。

说明:

smith计算出来的电感和实际有差距,可以理论计算出来尝试附近的值。应该不会差太远。匹配电路的

smith图尽量要使我们需要的频段能接近50Ω,而其他频段要尽量不要接近50Ω(也就是不需要的频段log Mag值-10db以上,这样做是为了不让其他频段串进来造成干扰。

8.5、相关QA

Q:匹配调试串并LC,smith图上不按理论轨迹行走?

- 对于射频电路来说,”导线”不在是导线,而是具有特征阻抗,射频传输线可以看成电阻、电容和电感构成的网络。因为电容和电感不是理想的,不是单纯的感抗和容抗,所以并或串不是按等阻抗或等导纳圆行走。

Q:匹配过程中选择元件遵循那些原则?

落地电容值不要过大,电容越大,容抗越小,信号容易流入

GND.电容电感值不要过小,因为存在误差,容值、感值越小,误差影响越小,影响批次的稳定性。

电容、电感值选常规值,方便替换和采购。

Q:IC到天线段的呢?

- 天线段的匹配已经完成,

IC至天线端匹配调节我们也需要将天线匹配网络最后的元件pad点出割断。将板放入外壳中,由IC进入测试模式,比如由IC打出1db的信号,在割断处使用频谱仪测量也应该收到1db的信号。